My area of interest is hardware (FPGA/ASIC) design, computer architecture, and embedded systems. I am currently working on my Master’s in Computer Engineering at Iowa State University. My major professor is Dr. Phillip Jones.

Education

Skills

Experiences

Jan 2023 – Current

Teaching Assistant

Iowa State University Department of Electrical and Computer Engineering

Ames, Iowa

Jan 2023 – Current

May 2025 – August 2025

Embedded Systems Intern

Eaton Corporation

Raleigh, North Carolina

May 2025 – August 2025

May 2024 – Aug 2024

Firmware Intern

Eaton Corporation

Rockville, Maryland

May 2024 – Aug 2024

Jan 2024 – May 2024

Research Assistant

Microarchitecture and Artificial Intelligence Security (MAIS) Lab

Ames, Iowa

Jan 2024 – May 2024

May 2023 – Aug 2023

Embedded System Intern

Eaton Corporation

Moon Township, Pennsylvania

May 2023 – Aug 2023

Aug 2022 – May 2023

Research Fellow

Institute for Transportation at Iowa State University

Ames, Iowa

Aug 2022 – May 2023

See my LinkedIn profile for details about my career! My socials:

Projects

Finding a 20+ Year Old Bug in a UPS System

- Skills: Formal Methods, Spin, Temporal Logic

- Date: September 2025 – December 2025

- Abstract: For the final project of COMS 507, I analyzed and formally verified, using model checking, a real-world Uninterruptible Power Supply (UPS) bypass state machine using the Spin model checker.

- Final Presentation:

Transformer Translation Model for English -> Mandarin

- Skills: PyTorch, Machine Learning

- Date: Apr 2025 – May 2025

- Partners: Justin Wenzel

- Abstract: For the final project of EE526, my partner and I worked on a transformer translation model as a pedagogical project. This is ongoing, please check back for details.

- GitHub: https://github.com/jona1115/trans2_encn/tree/main

SADD MaMA Rocket: RISC-V Sparse Matrix Multiplication For the Rocket Core

- Skills: Chipyard, Chisel, C

- Date: Oct 2024 – Dec 2024

- Partners: Steve Frana

- Abstract: Matrix multiplication is a fundamental operation in numerous computational domains. Much work has been done to implement general matrix multiplication accelerators, such as UCB’s Gemmini. However, the accelerator doesn’t support sparse matrix multiplication, which is very common in modern workloads like ML. This project proposed a sparse matrix multiplication accelerator inspired by Wang et al.’s SADD architecture.

HAML: Heterogeneous and Accelerated Computing for Machine Learning Algorithms

- Skills: C/C++, Petalinux

- Date: Jan 2024 – Dec 2024

- Partners: Josh Czarniak, Justin Wenzel, Kai Heng Gan, Santiago Campoverde

- Summary: Implement three machine learning (ML) models on an FPGA board with an ML accelerator. Achieve a throughput of 200FPS, as per client requirement.

- Website: https://sddec24-05.sd.ece.iastate.edu

Advanced Embedded Systems Projects

5-Stage MIPS Pipeline Processor

- Skills: Assembly, VHDL, ModelSim

- Date: Jan 2023 – May 2023

- Partners: Justin Wenzel, Reece Dodge

- Summary: Designed, verified, and optimized the performance and functionality of a 5-stage MIPS Pipeline Processor for the MIPS R2000 ISA. Developed the processor using VHDL and utilized QuestaSim for simulation and testing. Implemented advanced techniques such as forwarding, flushing, and stalling to achieve efficient instruction pipelining, resulting in a remarkable CPI (Cycles Per Instruction) between 1.1 and 1.3. Collaborated closely with the team to fine-tune the processor’s design, ensuring optimal performance and meeting project requirements.

- Website: https://sddec24-05.sd.ece.iastate.edu

Roomba Food Delivery Bot

- Skills: Embedded C

- Date: Oct 2022 – Dec 2022

- Partners: Justin Wenzel, Noah Mack, Caleb Lemmons

- Summary: Collaborated with a team of 5 to develop a food delivery bot using a Roomba as the base platform. Integrated components like a TI4C123 microcontroller, IR sensor, and radar sensor enable autonomous navigation and efficient delivery of food items. Designed and implemented a robust traffic detection system using radar and IR sensors, leveraging advanced algorithms and sensor fusion techniques to enhance the bot’s situational awareness.

Publication(s)

(Nov 2024) Systematical Evasion from Learning-based Microarchitectural Attack Detection Tools

- Journal: IEEE Journal on Emerging and Selected Topics in Circuits and Systems (Impact factor: 3.7)

- Authors: Debopriya Roy Dipta, Jonathan Tan, Berk Gulmezoglu

- Publish date: Nov 4, 2024

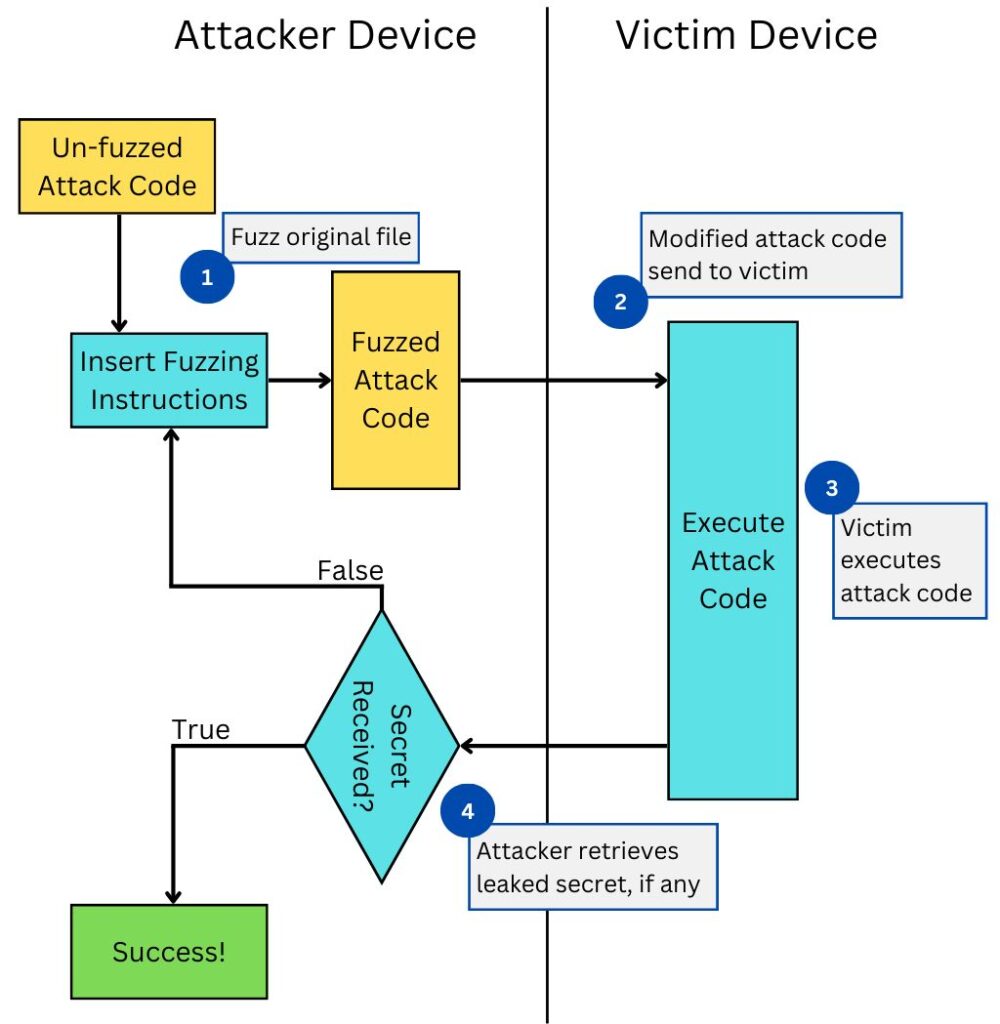

- Super summary: In this study, we evaluate the robustness of various ML-based detection models with a sophisticated fuzzing framework. The framework manipulates hardware performance counters in a controlled manner using individual fuzzing blocks. Later, the framework is leveraged to modify the microarchitecture attack source code and to evade the detection tools. We evaluate our fuzzing framework with time overhead, achieved leakage rate, and the number of trials to successfully evade the detection.

- Link: https://ieeexplore.ieee.org/document/10742379

- Featured on LinkedIn: Click me